嵌入式系统如何提高PCB信号的完整性

随着电子技术的不断进步,嵌入式系统将应用到越来越多的领域。 在这众多的应用中,人们考虑的不再是功能和性能,而是可靠性和兼容性。 那么,如何通过布线技术提高嵌入式系统PCB的信号完整性就成了一个“重要课题”。

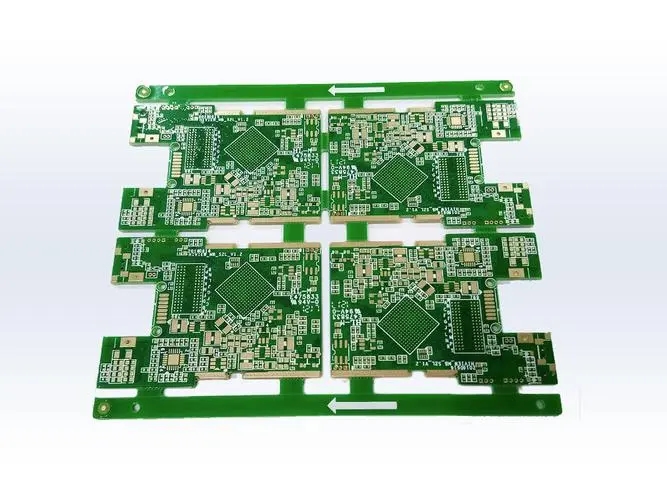

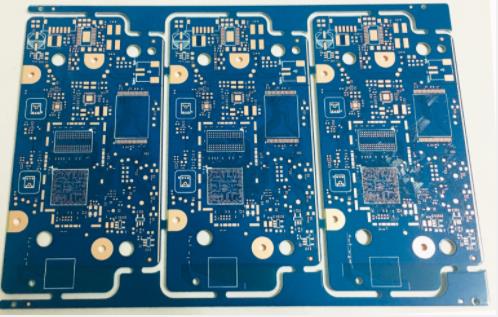

众所周知,PCB(印刷电路板)是电子产品中电路元器件的基本支撑,其设计质量往往直接影响嵌入式系统的可靠性和兼容性。 以往,在一些低速电路板中,时钟频率一般只有10MHz左右。 电路板或封装设计的主要挑战是如何在双层板上布线所有信号线,以及如何在组装过程中不损坏封装。

互连的电气特性并不重要,因为它们不会影响系统性能。 从这个意义上讲,低速信号电路板中的互连是平滑和透明的。 但随着嵌入式系统的发展,所用的电路基本都是高频电路。 随着时钟频率的增加,信号的上升沿也变短。 印制电路对通过信号的容抗和感抗会远大于印制电路本身的电阻,严重影响信号的完整性。 对于嵌入式系统,当时钟频率超过100MHz或上升沿小于1ns时,信号完整性的影响就变得很重要。

在PCB中,信号线是信号传输的主要载体。 信号线的走线将直接决定信号传输的优劣,从而直接影响到整个嵌入式系统的性能。 布线不合理会严重引起各种信号完整性问题,对电路产生时序、噪声和电磁干扰(EMI),严重影响嵌入式性能。 本文从高速数字电路中信号线的实际电气特性出发,建立电气特性模型,找出影响信号完整性的主要原因和解决问题的方法,以及应解决的问题。 并给出了接线时应遵循的方法和技巧。

信号完整性

信号完整性是指信号线上信号的质量,即信号在电路中以正确的时序和电压电平响应的能力。 具有良好信号完整性的信号是指在需要时具有所需的电压电平值。 信号完整性差不是单一因素造成的,而是板级设计中的多种因素造成的。 信号完整性问题体现在很多方面,主要有延迟、反射、串扰、过冲、振荡、地球炸弹等。

延时:延时是指信号在PCB板的传输线上以有限的速度传输,信号从发送端到接收端,其间存在传输延迟。 信号延迟会影响嵌入式时序; 传输延迟主要取决于导线的长度和导线周围介质的介电常数。 在高速数字系统中,信号传输线的长度是影响时钟脉冲相位差最直接的因素。 时钟脉冲相位差是指同时产生的两个时钟信号不同步到达接收端。 时钟脉冲的相位差降低了信号到达的可预测性。 如果时钟脉冲的相位差太大,接收端就会产生错误信号。

反射:反射是信号在信号线上的回波。 当信号延迟时间远大于信号跳跃时间时,必须将信号线视为传输线。 当传输线的特性阻抗与负载阻抗不匹配时,信号功率(电压或电流)的一部分传输到线路并到达负载,但也有一部分被反射。 如果负载阻抗小于原阻抗,则反射为负; 相反,反思是积极的。 布线几何形状的变化、不正确的接线端接、通过连接器的传输以及电源层的不连续性都会导致此类反射。

串扰:串扰是指由于两条信号线之间的耦合、信号线之间的互感和互容而引起的信号线上的噪声。 电容耦合导致耦合电流,而电感耦合导致耦合电压。 串扰噪声源于信号线之间、信号系统与配电系统之间以及过孔之间的电磁耦合。 串行绕组可能会造成时钟错误、间歇性数据错误等,影响相邻信号的传输质量。 现实中,串扰无法完全消除,但可以控制在系统能够承受的范围内。 PCB层数参数、信号线间距、驱动器和接收器的电气特性、基线端接方式等对串扰有一定的影响。

过冲和下冲:过冲是指超过设定电压的第一个峰值或谷值。 对于上升沿,指的是最高电压; 对于下降沿,它指的是最低电压。 Downrush 是指下一个超过设定电压的谷值或峰值。 过度的过冲会导致保护二极管工作,导致其过早失效。 过多的下冲会导致错误的时钟或数据错误(误操作)。

振荡和环绕振荡:振荡现象是重复的过冲和下冲。 信号振荡是由线路上传输的电感和电容引起的,属于欠阻尼状态,而周围振荡属于过阻尼状态。 与反射一样,振荡和环绕振荡也是由许多因素引起的。 振荡可以通过适当的终止来减少,但不能完全消除。

地电平弹跳噪声和回流噪声:当电路中有较大的电流浪涌时,会引起地电平弹跳噪声。 例如,当同时开启大量芯片输出时,会在芯片和电路板的电源层流过较大的瞬态电流,芯片封装和电源层的电感和电阻会导致 电源噪声,会在真实地平面上产生电压波动和变化,这种噪声会影响其他元件的动作。 负载电容的增大、负载电阻的减小、接地电感的增大、开关器件数量的增加都会导致接地弹簧的增大。

传输通道电气特性分析

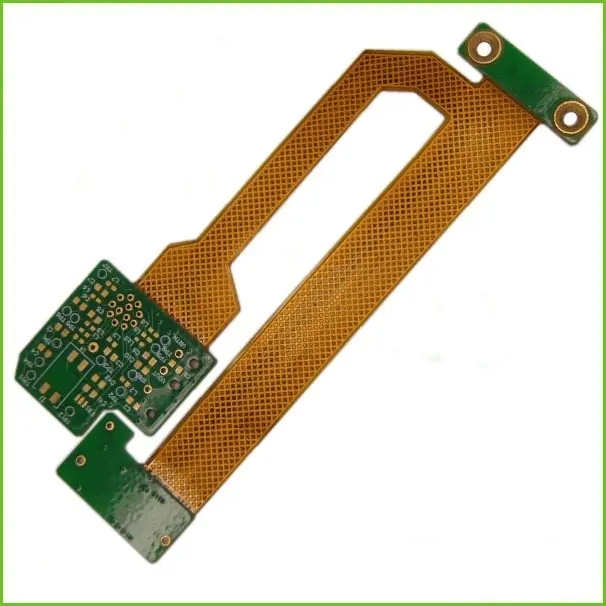

在多层PCB中,大多数传输线不仅布置在单层上,而是交错布置在多层上,各层之间通过过孔连接。 因此,在多层PCB中,典型的传输通道主要包括三部分:传输线、布线角和过孔。 在低频情况下,印制线和布线过孔可以看作是连接不同器件管脚的公共电气连接,不会对信号质量产生太大影响。 但在高频情况下,印制线、转角和过孔不仅要考虑它们的连通性,还要考虑它们在高频下的电气特性和寄生参数。

高速PCB传输线电气特性分析

在高速PCB的设计中,不可避免地要大量使用不同长度的信号连接线。 与信号本身的变化时间相比,信号通过连接线的延迟时间是不容忽视的。 信号以电磁波的速度在连接线上传输。 此时连接线是一个具有电阻、电容和电感的复杂网络,需要用分布参数系统模型即传输线模型来描述。

传输线用于将信号从一端传输到另一端。 它由两根一定长度的导线组成,一根称为信号通路,另一根称为返回通路。 在低频电路中,传输线的特性表现为纯电阻电气特性。 在高速PCB中,随着传输信号频率的升高,导体间的容性阻抗减小,而导体上的感性阻抗增大。 信号线将不再只表现出纯电阻,即信号不仅在导体上传输,而且在导体间的介质中传输。 如果信号频率进一步增加,当j ω L>>R,1/(j ω C) <对于均匀导体,传输线的电阻R、寄生电感L和寄生电容C的平均分布(即L1=L2= ...=Ln; C1=C2=...=Cn+1) 不考虑外界环境的变化。 PCB 制造商、PCB 设计人员和 PCBA 制造商将解释如何提高嵌入式系统中 PCB 信号的完整性。

然后

联系

电话热线

13410863085Q Q

微信

- 邮箱