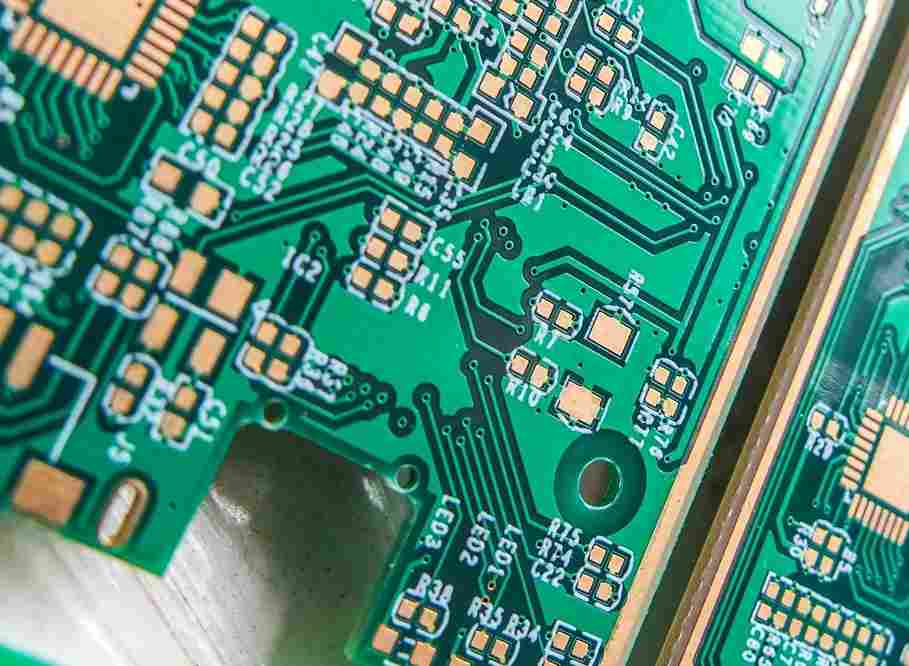

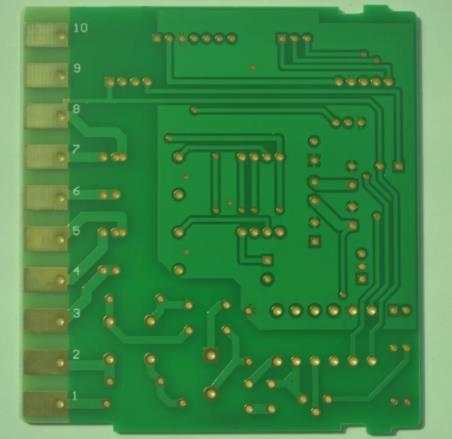

高速FPGA电路板设计要点

在电路板设计中,为了最大限度地减少串扰,微带线和带状线的布线可以遵循一些准则。 对于双带线布局,布线是在两层内板上进行,两侧都有电压参考平面。 此时,最好对与板相邻的所有导体都采用正交布线技术,以便最大化两个信号层之间的介质材料的厚度,最小化每个信号层与其相邻参考平面之间的距离 ,并保持所需的阻抗。

微带线或带状线布线指南

走线间距至少应为电路板布线层间介质层厚度的三倍; 最好提前使用模拟工具模拟其行为。为了最大限度地减少共模噪声的影响,关键的高速网络被差分拓扑取代。 在设计限制内,尽量匹配差分信号路径的正负引脚。减少单端信号的耦合影响,留有适当的间距(走线宽度的三倍以上),或者在不同的板上走线(相邻层相互正交)。 另外,使用仿真工具也是满足间距要求的好方法。将信号终端信号之间的并行长度减少到最小。

同时转换噪声

当时钟和I/O数据速率增加时,输出跳变次数相应减少,信号路径放电和充电期间的瞬态电流相应增加。 这些电流可能会导致板级地弹,即地电压/Vcc瞬间上升/下降。 非理想电源的瞬间大电流会导致Vcc瞬时下降(Vcc drop或sag)。 以下是一些好的电路板设计规则,有助于减少这些同步转换噪声的影响。

将未使用的 I/O 引脚配置为输出引脚,并以低电压驱动它们以减少接地反弹。尽量减少同时转换输出引脚的数量,并使它们均匀分布在整个FPGA I/O部分。当不需要高边沿速率时,FPGA 输出选择低转换速率。Vcc插在多层板的接地面之间,以消除高速走线对各层的影响。将所有板层用于Vcc和接地可以最小化这些平面的电阻和电感,从而提供具有较低电容和噪声的低电感源,并在与这些平面相邻的信号层上返回逻辑信号。

预加重和平衡

最先进FPGA的高速收发器能力使其成为高效的可编程系统级芯片组件,同时也给电路板设计人员带来了独特的挑战。 一个关键问题,特别是与布局相关的问题,是与频率相关的传输损耗,这主要是由集肤效应和介电损耗引起的。 当高频信号在导体表面(如PCB走线)传输时,由于导线的自感应,会产生集肤效应。 这种效应减少了导线的有效导电面积,削弱了信号的高频成分。 介电损耗是由层间介电材料的电容效应引起的。 集肤效应与频率的平方根成正比,而介电损耗与频率成正比; 因此,介电损耗是高频信号衰减的主要损耗机制。

数据速率越高,集肤效应和介电损耗越严重。 对于 1Gbps 系统,链路上信号电平的降低是可以接受的,但对于 6Gbps 系统则不然。 然而,目前的收发器都具有发射机预加重和接收机均衡功能,可以补偿高频通道的失真。 它们还可以增强信号完整性并放宽走线长度的限制。 这些信号调节技术可延长标准 FR-4 材料的使用寿命,并支持更高的数据速率。 由于 FR-4 材料中的信号衰减,当以 6.375Gbps 运行时,允许的走线长度仅限于几英寸。 预加权和均衡功能可以将其扩展到40英寸以上。

一些高性能FPGA集成了可编程预加重和均衡功能,例如Stratix II GX器件,因此可以使用FR-4材料,放宽最大走线长度等布局限制,并降低电路板成本。 预加重功能可以有效改善信号的高频成分。 Stratix II GX 中的 4 抽头预加重电路可以减少信号分量的散射(从一位到另一位的空间扩展)。 预加重电路可提供最大500%的预加重,每个抽头可根据数据速率、走线长度和链路特性优化至最多16级。

Stratix II GX 接收器包含增益级和线性均衡器,以补偿信号衰减。 除了输入增益级之外,该器件还允许电路板设计人员拥有最大 17dB 的均衡水平,可以使用 16 个均衡器级中的任意一个来克服电路板损耗问题。 均衡和预加重可以在音乐会环境中使用,也可以单独使用以优化特定链接。

当系统运行时,或者当卡插入背板或其他机箱后进行配置时,设计人员可以更改 Stratix II GX FPGA 中的预加重和均衡级别。 这使系统设计人员能够灵活地自动将预加重和均衡级别设置为预定值。 另外,这些值还可以根据单板插入机箱或背板的槽位动态确定。

EMI问题及调试

印刷电路板引起的电磁干扰与电流或电压随时间的变化以及电路的串联电感成正比。 高效的电路板设计可以最大限度地减少 EMI,但可能无法完全消除它。 消除“入侵”或“热”信号,并正确参考地平面来发送信号,也有助于降低 EMI。 最后,使用当今市场上常见的表面贴装元件也是降低 EMI 的一种方法。

然后

联系

电话热线

13410863085Q Q

微信

- 邮箱