PCB生产使用正确的设计工具来避免PCB布局错误

印刷电路板的布局是一项困难而艰巨的任务,请不要让别人告诉你。 电路必须按照严格的规则进行结构设计,才能以最高性能运行,同时必须遵循另一组设计规则以实现可制造性。 即使是小型且“简单”的布局也会带来独特的设计挑战,PCB 布局工程师必须配备最新的工具来完成他们的工作。

PCB 设计的 CAD 工具是软件工程的奇迹。它们具有许多不同的特性和功能,以便布局设计师可以完成他们的工作。 这些范围从实用程序到初始设置布局的设计,再到高级跟踪路由引擎,以完成原理图的所有网络连接。 为了充分利用这些工具,设计人员必须了解 PCB 布局的所有细微差别,尤其是那些如果处理不当可能导致问题的细微差别。 以下是设计人员应注意的一些常见 PCB 布局错误。

准备设计:您准备好进行 PCB 布局了吗?

当新设计准备好布局时,很自然地开始放置组件和布线轨道。 这样做的问题是,在布局开始之前,您通常需要做大量的准备工作。 许多设计师陷入了“我稍后再处理”的陷阱,但却发现他们现在有更大的问题需要纠正,如果他们准备得更好,这些本来是可以避免的。 以下是一些常见问题。 如果你提前解决掉这些问题,以后就可以避免很多麻烦。

过时或不正确的元件:原理图元件出现问题的情况并不少见。 如果他们从早期设计中复制电路,或者库不是最新的,或者使用实际上过时的组件的集合,则最终结果将是相同的。 这些组件可能无法用于制造,因此需要重新设计以更新零件。 清理BOM中的此类错误或使用库服务中的零件可以解决此问题。

不正确的设计同步:有时,即使原理图数据库未与布局完全同步,设计工作也会开始。 这样做有很多令人信服的理由,其中节省时间排在第一位,但效果往往很差。 同步问题必须稍后纠正,这可能会导致整个电路的某些部分被撕裂。 这里的教训是花一些时间把它做好,然后花太多时间在布局上。

电路板层堆叠配置:众所周知,在层堆叠最终确定之前,设计者就会开始对电路板进行布局。 同样,这通常是为了节省时间,但这些良好的意图可能会适得其反。 布局开始后,在 CAD 系统中移动图层可能需要一些时间,并且可能会导致设计错误。 然而,更大的问题是将已完成的布线从一层移至另一层是否会影响电路板的整体信号完整性。 您可能会发现自己必须重新设计电路的一些主要部分才能纠正这些问题。

设计参数:在开始布局之前未能完全设置PCB设计CAD系统可能不会引入设计错误,但可能会减慢您的速度。 颜色、网格和许多其他参数旨在创建一个有助于提高生产力的工作环境,如果您在开始之前不配置这些参数,那么您只会伤害自己。 其中许多设置可以在模板或自述文件中传输,这在开始新设计时非常有用。

此时,电路板已准备好开始布局。 接下来,我们将检查元件放置过程中可能发生的一些常见错误。

放置元件时 PCB 布局错误:

面对现实吧。 虽然可能很复杂,但 PCB 布局也很有趣。 操纵屏幕上的组件并用网状连接橡皮筋将它们绑定是您可以解决的最好和最具挑战性的问题之一。 然而,就像在放置电路板之前进行设置一样,如果您不采取预防措施,则存在一些潜在的问题,可能会导致您的设计出现许多问题。 让我们从一个涉及您将放置在板上的物理足迹的潜在问题开始。

不正确的封装:我们已经讨论了在设计中使用正确组件的重要性,但是如果这些组件使用不正确的封装,您仍然会遇到问题。 尽管从技术上讲,这应该在设计同步期间发现,但设计人员应确保他们使用正确的封装。 无论是用PQFP取代BGA还是电容极性接反,如果没有立即发现此类错误,都需要重新设计。

不要忽视规划:为了确保良好的信号和电源完整性,PCB设计电路必须仔细划分,以达到最佳性能。 对于每毫米空间都很重要的高密度设计尤其如此。 未能做到这一点的设计人员可能需要昂贵的重新设计来提高电路板的性能。 使用原理图放置逻辑组的组件或在电路板上指定放置空间对于防止分区错误非常有帮助。

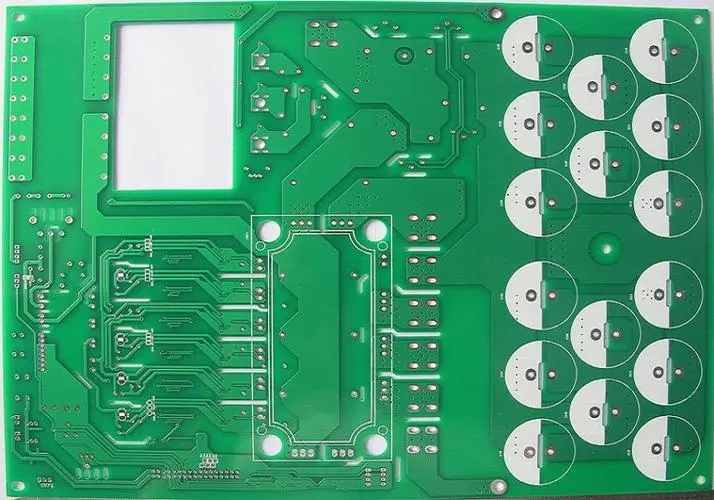

DFM 至关重要:确保电路板的可制造性与设计中的信号和电源完整性同样重要。 PCB 设计人员在设计时遵循布局可制造性 (DFM) 规则至关重要。 这包括自动组装设备和测试设备的组件之间的最小间距,以及技术人员调试和返工电路板的空间。 在 CAD 工具中使用设计规则和约束对于消除 DFM 错误是绝对必要的。

请记住设计 PDN:虽然电路板布局对于确保良好的信号完整性至关重要,但关注电力传输网络 (PDN) 同样重要。 在布局电源组件时,设计人员可以轻松地在设计中引入噪声和其他干扰。 确保遵循良好的 PDN 设计准则,并使用 CAD 系统的电源完整性工具检查错误。

最后,电路板就可以接线了,但是请不要放松警惕。 如果不小心,错误仍可能蔓延到设计中。

PCB布局上的布线是一项非常有意义的任务。 每个路由完成后,其对应的网络连接指南都会被消除,以便您进一步完成工作。 设计错误也很容易传播,因为它们可能会破坏你正在尝试完成的工作,因此设计师必须保持警惕。 以下是一些需要注意的示例。

逃逸布线:表面贴装器件需要将电线从焊盘布线到通孔,以便在电路板的其他层上互连。 这称为逃逸路由或扇出路由,这对于大多数 SMT 设备来说非常简单。 然而,小间距的高引脚数器件提出了更大的挑战。 设计人员必须小心,不要通过逃逸孔阻塞内层的布线通道。 通常,芯片制造商会在其产品数据表中发布推荐的布线解决方案,这可以帮助您避免布线拥塞。

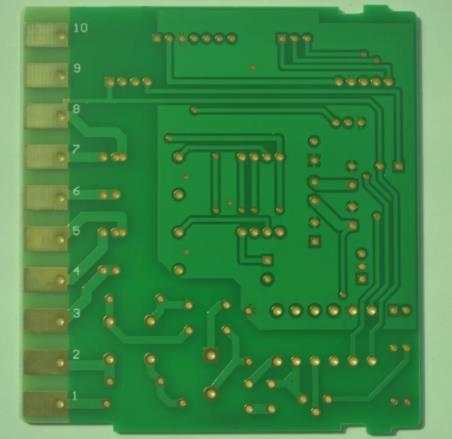

约束管理:鉴于当今电路板设计的所有不同要求,布局设计人员必须充分利用其设计约束管理系统。 这些实用程序允许您为一个网络或一组网络配置必要的布线宽度和间距,并为组件分配间隙规则。 他们甚至可以通过设置高速设计拓扑、通孔类型和电气时序参数来走得更远。 在上图中,您可以看到设计约束管理系统中可用的一些设置,以防止违反布线规则。

布线空间不够:对布线图案密集的电路板进行布线时,提前规划布线位置非常重要。 这将确保有足够的空间来容纳双倍数据速率 (DDR) 布线常见的高密度图案。 如果没有这样的计划,您可能会发现需要更换和重新布线大部分电路板。 许多 CAD 工具(例如 Cadence 的 Allegro PCB 编辑器)都提供布线模式来帮助完成此类规划任务。

缺乏参考平面:随着电路板设计中信号速度的提高,PCB布局具有足够的参考平面至关重要。 如果没有这些平面,高速传输线和其他敏感网络可能没有清晰的信号传输。

然后

联系

电话热线

13410863085Q Q

微信

- 邮箱